Why Strober

Existing Methodology

|

Silicon Prototype |

µarch Simulation + Analytic Power Modeling |

RTL/Gate-level Simulation |

| e.g. |

Raven |

gem5 + McPAT |

Synopsys VCS |

| Pros |

Most Accurate, Fast |

- Flexible, Easy to use

- Early Design Space Exploration

|

Extremely Accurate |

| Cons |

Long wait for silicon back |

- Validation against real systems

- Much slower than real systems(<400KHz)

|

Painfully Slow(<10KHz) |

Features

- Fast: orders of magnitude speedup over SW simulation

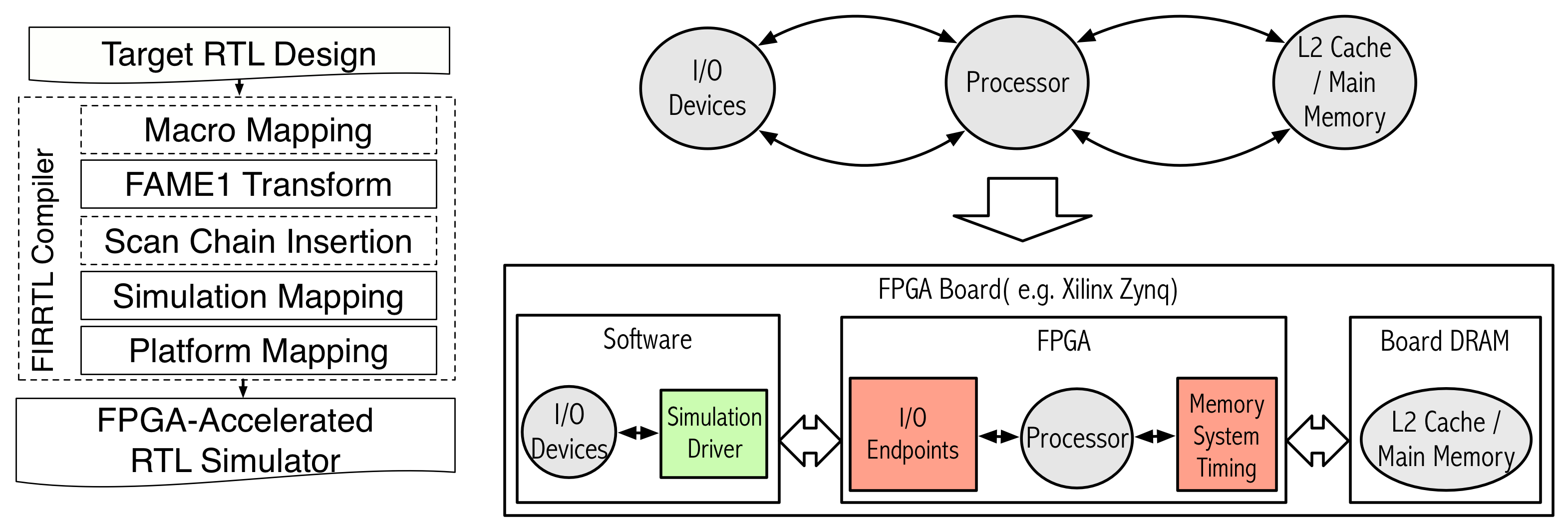

- Easy to use: automatically generates FPGA-Accelerated RTL simulators

- Accurate: < 5% errors with 99% confidence.

Sample-based Energy Simulation

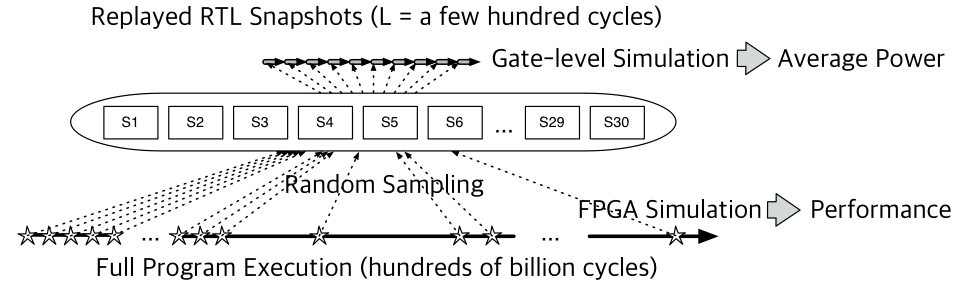

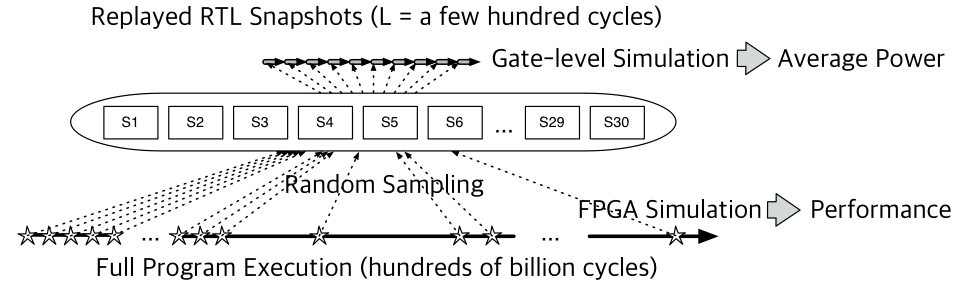

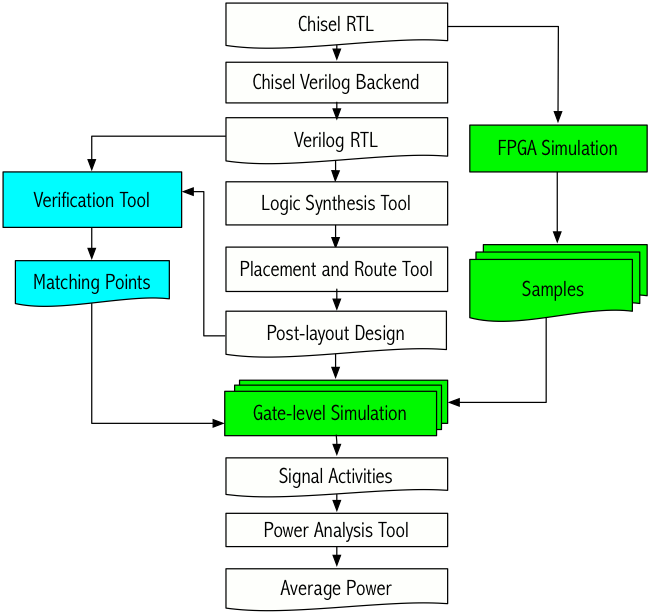

Sample-based energy simulation accurately and quickly estimates performance and average power by obtaining random RTL state sample snapshots

from fast simulations and replaying the sample snapshots on slow but detailed simulations.

The central limit theorem states that

the sampling error depends only on the sample size and the variance of execution, not on the length of execution.

Thus, the longer we simulate the target designs, the more speedup we can achieve through this methodology.

The Strober Framework

FPGA Simulator

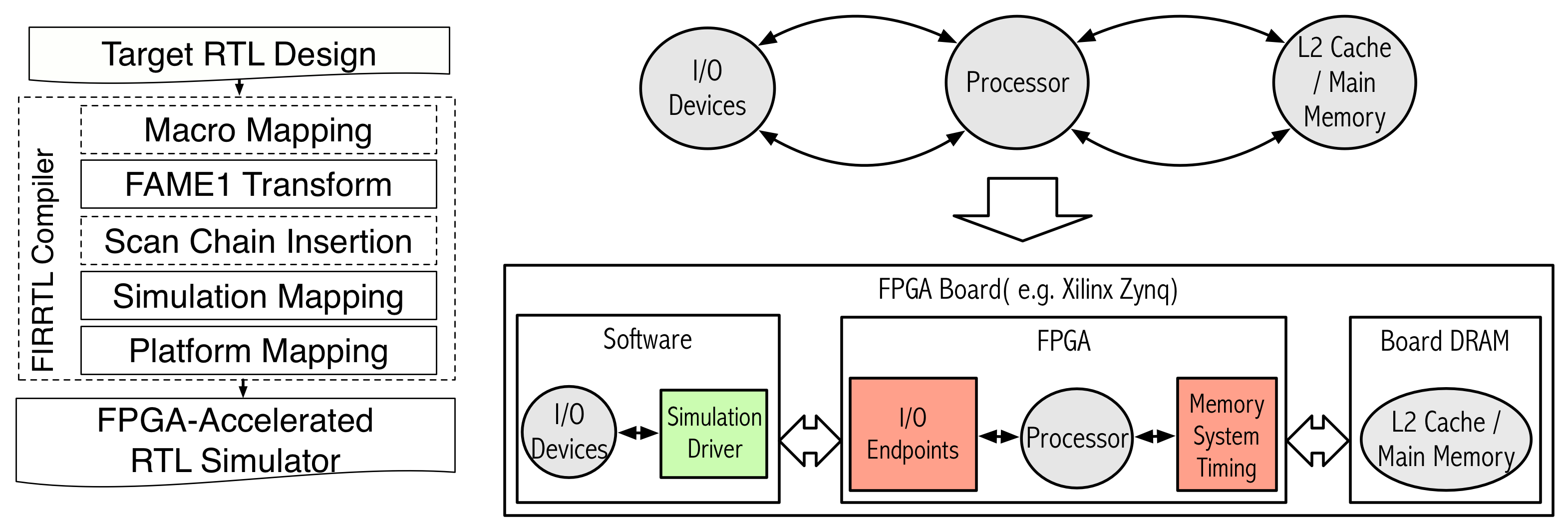

Strober is an implementation of sample-based energy simulation developed in UC Berkeley. Strober is built upon Chisel, taking advantage of hardware generators and custom transforms. Strober automatically generates FPGA performance simulators from arbitrary RTL designs written in Chisel, thus minimizing the designers' manual efforts. Strober also adds scan chains and I/O trace buffers to read out the RTL state sample snapshots from the FGPA simulation.

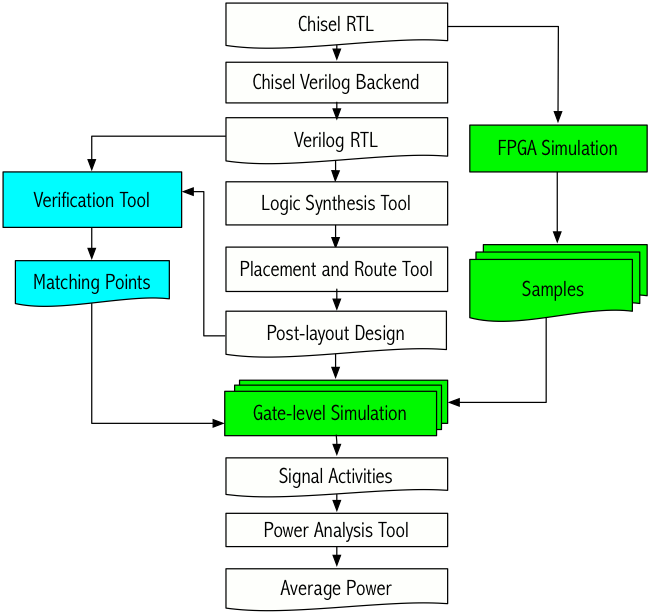

Sample Replay

The random RTL state sample snapshots are replayed on gate-level simulation for the average power estimation. The replay tool flow is built using industry-standard CAD tools, widely available to academic research through academic license programs . Strober provides custom VPI routines to replay the RTL state snapshots on gate-level simulation by using the matching points from the formal verification tool.

Publication

- "Strober: Fast and Accurate Sample-Based Energy Simulation for Arbitrary RTL", Donggyu Kim, Adam Izraelevitz, Christopher Celio, Hokeun Kim, Brian Zimmer, Yunsup Lee, Jonathan Bachrach, Krste Asanovic, The 43rd International Symposium on Computer Architecture (ISCA), Seoul, Korea, June 2016.

- "Evaluation of RISC-V RTL with FPGA-Accelerated Simulation", Donggyu Kim, Christopher Celio, David Biancolin, Jonathan Bachrach, Krste Asanovic, The First Workshop on Computer Architecture Research with RISC-V (CARRV), Boston, MA, October 2017.

Source Code

Strober is available as a plug-in of MIDAS